FPGA入门 —— DDR3(MIG IP 核) 入门 DDR3 基本内容简介 DDR 简介 DDR=Double Data Rate双倍速率同步动态随机存储器。严格的说DDR应该叫DDR SDRAM,人们习惯称为DDR,其中,SDRAM 是Synchronous Dynamic Random ...

”DDR3 MIG“ 的搜索结果

VC707_MIG_DDR3.sim文件夹中是仿真的文件:testbench和DDR3模型参数VC707_MIG_DDR3.srcs文件夹中是源文件,包含DDR3的控制、收发模块、顶层文件

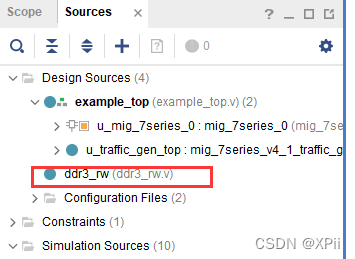

近期学习使用Verilog编写DDR3接口的读写测试,在编写过程中遇到许多问题,最终还是功夫不负,实现了DDR3数据写入和数据读取功能。这是完整的工程文件,可以直接进行仿真测试。

利用vivado的MIG控制器来实现DDR3的读写

快速上手Xilinx DDR3 IP核----汇总篇

DDR3 MIG IP核解决方案 信号方向描述app_addr [ADDR_WIDTH - 1:0]输入该输入指示当前请求的地址。app_cmd [2:0]输入该输入选择当前请求的命令。app_en输入这是app_addr [],app_cmd [2:0],app_sz和app_hi_pri...

通过实际项目的验证,DDR3 MIG XILINX FPGA已经证明了其在大数据处理场景中的重要作用。而基于Verilog代码实现的DDR3 MIG XILINX FPGA能够有效地管理存储器的读写操作,并通过FIFO接口进行数据的传输。DDR3 MIG ...

FPGA开源工作室将通过五篇文章来给大家讲解xilinx FPGA 使用mig IP对DDR3的读写控制,旨在让大家更快的学习和应用DDR3。 本实验和工程基于Digilent的Arty Ar...

本节主要是介绍 Xilinx DDR 控制器 IP 的创建流程、IP 用户使用接口 native 协议介绍和IP 对应的 Example Design 的仿真和上板验证。

对于移植别人工程时,需要留意这一点,用两种方式,第一种可以与硬件确认提供的时钟,但是一般这种都是fpga开发者在顶层通过PLL生成的200m时钟 ,另一种方式可以通过旧工程的MIG IP的xdc约束文件去确认下。...

文档介绍了如何将Xilinx DDR3 MIG IP核封装成FIFO接口,以便于在图像处理等场景中存储和处理大量数据。内容包括设计思路、状态机实现、读写FIFO配置、顶层模块连接以及仿真测试。通过封装,简化了读写操作,增加了...

本文介绍了如何使用MIG IP的AXI_FULL接口封装FIFO,以替代以太网传输图片工程中的DDR3读写控制模块。文档详细阐述了MIG IP的AXI_FULL接口生成、参数设置、读写控制模块设计思路和实现细节。通过仿真验证了模块的正确...

DDR3 MIG IP核

标签: fpga开发

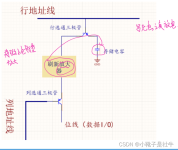

MIG IP 核是 Xilinx 公司针对 DDR 存储器开发的 IP,里面集成存储器控制模块,实现 DDR 读写操作的控制流程,下图是 7 系列的 MIG IP 核结构框图。MIG IP 核对外分出了两组接口。左侧是用户接口,就是用户( FPGA)...

Memory Interface Generator (MIG 7 Series)是 Xilinx 为 7 系列器件提供的 Memory 控制器 IP,使用该 IP 可以很方便地进行 DDR3 的读写操作。本文主要记录 Xilinx DDR3 MIG IP 的仿真过程,包括 IP 配置和 DDR3 ...

DDR3 SDRAM(Double Data Rate 3 Synchronous Dynamic RAM),即第三代双倍速率同步动态随机存储器。本系列文章尝试剖析缓存技术的基础原理,并通过FPGA进行实现。

常见有:SRAM、SDRAM、DRAM、DDR。其中,SRAM是静态存储器,不需要刷新电路来保存内部数据;DRAM是动态随机存储器,需要不断的刷新电路来保存数据。ROM:只读存储器。事先写好的,里面的数据不可更改,只能进行读...

文章介绍了在Xilinx FPGA上使用DDR3内存的方法,推荐使用官方MIG IP进行设计。详细说明了在Vivado中配置MIG IP的步骤,包括时钟设置、内存类型选择、控制器选项、FPGA选项等。强调了时钟配置的重要性,并提供了对MIG...

DDR3 MIG XILINX FPGA verilog代码,顶层接口封装为fifo,使用简单方便,主要用于大数据量的缓冲,已实际应用在多个项目上

文章结尾包含此专栏文章详细目录。...该专栏包括:MIG的硬件设计讲解,IP底层代码讲解(lut和时钟资源占用,初始化,写入均衡,ZQ校准),app接口和AXIfull接口代码讲解,仿真环境搭建以及讲解,各种DMA示例教程等。

DDR3基本内容介绍 1,DDR3简介 DDR3全称double-data-rate 3 synchronous dynamic RAM,即第三代双倍速率同步动态随机存储器。所谓同步,是指DDR3数据的读取写入是按时钟同步的;所谓动态,是指DDR3中的数据掉电...

Xilinx vivado DDR3 MIG IP核解决方案以及应用

推荐文章

- 大数据技术未来发展前景及趋势分析_大数据技术的发展方向-程序员宅基地

- Abaqus学习-初识Abaqus(悬臂梁)_abaqus悬臂梁-程序员宅基地

- 数据预处理--数据格式csv、arff等之间的转换_csv转arff文件-程序员宅基地

- c语言发送网络请求,如何使用C+发出HTTP请求?-程序员宅基地

- ccc计算机比赛如何报名,整理:加拿大的CCC是什么,怎么报名?-程序员宅基地

- RK3568 学习笔记 : ubuntu 20.04 下 Linux-SDK 镜像烧写_rk3568刷linux-程序员宅基地

- Gradle是什么_gradle是干嘛的-程序员宅基地

- adb命令集锦-程序员宅基地

- 【Java基础学习打卡15】分隔符、标识符与关键字_java分隔符有哪三种-程序员宅基地

- Python批量改变图片名字_python批量修改图片名称-程序员宅基地